# Blitz-64

# Instruction Set Architecture Reference Manual

ISA Version: 2.0

Harry H. Porter III Portland State University

HHPorter3@gmail.com

23 April 2023

This document describes the Instruction Set Architecture (ISA) for the Blitz-64 processor core. It documents all the machine instructions as well as the assembly code notation for these instructions.

# **Table of Contents**

| List of Instructions                           | 6  |

|------------------------------------------------|----|

| Chapter 1: Introduction                        | 11 |

| Quick Summary                                  | 11 |

| Instruction Set Architectures                  | 11 |

| Goals and Principles: Personal Statements      | 12 |

| Document Revision History / Permission to Copy | 17 |

| Relevant Software Tools                        | 17 |

| Chapter 2: Terminology and Notation            | 19 |

| Quick Summary                                  | 19 |

| Kilo and Mega Prefixes                         | 19 |

| Bits and Bytes                                 | 20 |

| Main Memory                                    | 23 |

| Big Endian                                     | 23 |

| Alignment                                      | 26 |

| Signed Numbers                                 | 27 |

| Sign-Extension                                 | 30 |

| Size Reduction                                 | 31 |

| Chapter 3: Architectural Summary               | 32 |

| Quick Summary                                  | 32 |

| Memory, Addresses, and Memory-Mapped I/O       | 33 |

| The Processor State                            | 34 |

| The Registers                                  | 34 |

| Control and Status Registers (CSRs)            | 38 |

| Virtual Memory                                 | 39 |

| <b>Chapter 4: Instruction Formats</b>          | 41 |

| Quick Summary                                  | 41 |

| Compressed and Full-Sized Instructions         | 41 |

| Opcode Encoding                                | 42 |

| Instruction Fields                             | 43 |

| Instruction Formats                            | 44 |

| Operand Syntax                                 | 46 |

| Chapter 5: Instructions                              | 48  |

|------------------------------------------------------|-----|

| Machine Instructions versus Synthetic Instructions   | 48  |

| All Instructions - Summary Listing                   | 49  |

| Machine Instructions, Grouped By Format              | 55  |

| The Instruction Set                                  | 60  |

| Instruction Opcodes                                  | 138 |

| Miscellaneous Remarks                                | 144 |

| Chapter 6: Privileged Instructions and Kernel Mode   | 146 |

| Quick Summary                                        | 146 |

| Privileged Instructions                              | 146 |

| Control and Status Registers                         | 147 |

| Chapter 7: Exceptions, Interrupts, and Trap Handling | 159 |

| Quick Summary                                        | 159 |

| Traps, Exceptions, and Interrupts                    | 159 |

| Interrupt Processing                                 | 164 |

| Description of Exceptions                            | 166 |

| The Singlestep Exception                             | 182 |

| Value of Saved PC                                    | 185 |

| Traps Related to Instruction Fetching                | 186 |

| Trap Priority and Simultaneous Exceptions            | 188 |

| Pending Interrupts                                   | 194 |

| Delegation to User Mode Error Handlers               | 196 |

| Trap Processing and Handler Startup                  | 197 |

| Saving State During Thread Switching                 | 199 |

| Global Trap Handler — Dispatching and Return         | 201 |

| Chapter 8: Memory, Address Spaces, and Page Tables   | 208 |

| Quick Summary                                        | 208 |

| Memory Organization                                  | 209 |

| Tasks, Address Spaces, and the User Mode Viewpoint   | 211 |

| Page Tables                                          | 214 |

| Virtual Addresses                                    | 224 |

| Page Table Entries                                   | 225 |

| MMU: Basic Operation                                 | 227 |

#### **Table of Contents**

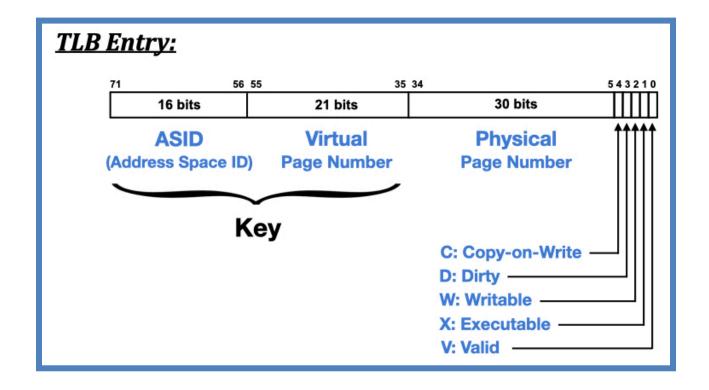

| TLB: Translation Lookaside Buffer               | 233 |

|-------------------------------------------------|-----|

| Comments                                        | 237 |

| Shared Core Functions                           | 241 |

| Private and Shared Memory                       | 244 |

| LOAD / STORE Atomicity                          | 245 |

| A Relaxed Memory-Model                          | 246 |

| FENCE and Memory Synchronization                | 248 |

| Invalidating Data in the Pipeline               | 259 |

| Out-of-Date TLB Registers                       | 262 |

| Chapter 9: Power-On-Reset and the Boot Sequence | 264 |

| Quick Summary                                   | 264 |

| Power-On-Reset                                  | 264 |

| The BootLoader Program                          | 265 |

| Security Issues Around Booting                  | 270 |

| Simple Systems                                  | 273 |

| Multi-Stage Boot Processes                      | 275 |

| The Secure Storage Area                         | 277 |

| Chapter 10: Memory-Mapped I/O                   | 287 |

| Quick Summary                                   | 287 |

| Overview                                        | 287 |

| Boot ROM Area                                   | 288 |

| Secure Storage Area                             | 289 |

| Simple Serial Communication                     | 291 |

| DMA Controller                                  | 294 |

| UART Serial Comm                                | 305 |

| Simple Disk                                     | 306 |

| Lock Controller                                 | 307 |

| Digital I/O Pins and LEDs                       | 311 |

| HDMI, USB, WiFi, etc.                           | 312 |

| MicroSD Card Slot                               | 312 |

| Adjacent Core Links                             | 313 |

| Appendix 1: Assembly Language                   | 316 |

| Assembling and Linking                          | 316 |

| Assembler Syntax                                | 317 |

#### **Table of Contents**

| Pseudo-Ops                         | 319 |

|------------------------------------|-----|

| Symbols                            | 322 |

| Segments and Linking               | 324 |

| The Global Pointer Register, gp    | 328 |

| Appendix 2: Implementation Details | 331 |

| Example: The Emulator              | 332 |

| Appendix 3: Recent Changes         | 336 |

| Acronym List                       | 343 |

| About the Author                   | 344 |

| ADD RegD,Reg1,Reg2                                                 | 60 |

|--------------------------------------------------------------------|----|

| ADDI RegD,Reg1,immed-16                                            | 60 |

| SUB RegD,Reg1,Reg2                                                 | 60 |

| *MUL RegD,Reg1,Reg2                                                | 60 |

| DIV RegD,Reg1,Reg2                                                 | 60 |

| REM RegD,Reg1,Reg2                                                 | 60 |

| AND RegD,Reg1,Reg2                                                 | 60 |

| ANDI RegD,Reg1,immed-16                                            | 60 |

| OR RegD,Reg1,Reg2                                                  | 60 |

| ORI RegD,Reg1,immed-16                                             | 60 |

| XOR RegD,Reg1,Reg2                                                 | 60 |

| XORI RegD,Reg1,immed-16                                            | 60 |

| MULADD RegD,Reg1,Reg2,Reg3 RegD ← (Reg1 × Reg2) + Reg3             | 61 |

| MULADDU RegD,Reg1,Reg2,Reg3 RegD ← (Reg1 × Reg2) + Reg3 (unsigned) | 61 |

| *NEG RegD,Reg1                                                     | 65 |

| *BITNOT RegD,Reg1                                                  | 65 |

| *NOP <no operands=""></no>                                         | 66 |

| *ABS RegD,Reg1                                                     | 66 |

| *MOV RegD,Reg1                                                     | 66 |

| *MOVI RegD,immediate                                               | 67 |

| SLL RegD,Reg1,Reg2 Shift left logical                              | 68 |

| SLLI RegD,Reg1,immed-6                                             | 68 |

| SLA RegD,Reg1,Reg2 Shift left arithmetic                           | 68 |

| SLAI RegD,Reg1,immed-6                                             | 68 |

| SRL RegD,Reg1,Reg2 Shift right logical                             | 68 |

| SRLI RegD,Reg1,immed-6                                             | 68 |

| SRA RegD,Reg1,Reg2 Shift right arithmetic                          | 68 |

| SRAI RegD,Reg1,immed-6                                             | 68 |

| ROTR RegD,Reg1,Reg2 Rotate right (circular)                        | 68 |

| ROTRI RegD,Reg1,immed-6                                            | 68 |

| SEXTB RegD,Reg1 Sign extend byte to 64 bits                        | 69 |

| SEXTH RegD,Reg1 Sign extend 16 bits to 64 bits                     | 69 |

| SEXTW RegD,Reg1 Sign extend 32 bits to 64 bits                     | 69 |

| NULLTEST Reg1 Trap if reg contains NULL                            | 70 |

| CHECKB Reg1 Trap if reg not within -128 +127                       | 70 |

| CHECKH Reg1 Trap if reg not within -32768 +32767                   | 70 |

| CHECKW Reg1 Trap if reg not within 32 bit range                    | 70 |

| ENDIANH RegD,Reg1 Reorder bytes in all 4 halfwords                 | 70 |

| ENDIANW RegD,Reg1 Reorder bytes in both words                      | 70 |

| ENDIAND RegD,Reg1 Reorder bytes in a doubleword                    | 71 |

| TESTEQ RegD,Reg1,Reg2 RegD $\leftarrow$ (Reg1 = Reg2) ? 1 : 0      | 71 |

| TESTNE RegD, Reg1, Reg2 RegD $\leftarrow$ (Reg1 $\neq$ Reg2)? 1:0  | 71 |

| TESTET RegD, Reg1, Reg2 RegD $\leftarrow$ (Reg1 < Reg2)? 1:0                        | 71 |

|-------------------------------------------------------------------------------------|----|

| TESTLE RegD,Reg1,Reg2 RegD $\leftarrow$ (Reg1 $\leq$ Reg2) ? 1:0                    | 71 |

| TESTEQI RegD,Reg1,immed-16 RegD $\leftarrow$ (Reg1 = immed) ? 1 : 0                 | 71 |

| TESTNEI RegD,Reg1,immed-16 RegD $\leftarrow$ (Reg1 $\neq$ immed) ? 1 : 0            | 71 |

| TESTLTI RegD,Reg1,immed-16 RegD $\leftarrow$ (Reg1 < immed) ? 1:0                   | 71 |

| TESTLEI RegD,Reg1,immed-16 RegD $\leftarrow$ (Reg1 $\leq$ immed) ? 1:0              | 71 |

| TESTGTI RegD,Reg1,immed-16 RegD $\leftarrow$ (Reg1 > immed) ? 1 : 0                 | 72 |

| TESTGEI RegD,Reg1,immed-16 RegD ← (Reg1 ≥ immed)? 1:0                               | 72 |

| *TESTGT RegD,Reg1,Reg2 RegD $\leftarrow$ (Reg1 > Reg2) ? 1 : 0                      | 72 |

| *TESTGE RegD,Reg1,Reg2 RegD ← (Reg1 ≥ Reg2)?1:0                                     | 72 |

| *TESTEQZ RegD,Reg1 RegD $\leftarrow$ (Reg1 = 0) ? 1 : 0, i.e., if zero              | 72 |

| *TESTNEZ RegD,Reg1 RegD $\leftarrow$ (Reg1 $\neq$ 0) ? 1 : 0, i.e., if non-zero     | 72 |

| *TESTLTZ RegD,Reg1 RegD $\leftarrow$ (Reg1 < 0) ? 1 : 0, i.e., if negative          | 72 |

| *TESTLEZ RegD,Reg1 RegD $\leftarrow$ (Reg1 $\leq$ 0) ? 1 : 0, i.e., if non-positive | 72 |

| *TESTGTZ RegD,Reg1 RegD $\leftarrow$ (Reg1 > 0)? 1:0, i.e., if positive             | 72 |

| *TESTGEZ RegD,Reg1 RegD $\leftarrow$ (Reg1 $\geq$ 0) ? 1 : 0, i.e., if non-negative | 72 |

| *LOGNOT RegD,Reg1 RegD $\leftarrow$ (Reg1 = 0) ? 1 : 0                              | 73 |

| ADDOK RegD,Reg1,Reg2 RegD $\leftarrow$ (Reg1+Reg2 overflows)? 0:1                   | 73 |

| ADD3 RegD,Reg1,Reg2 RegD ← Reg1+Reg2+Reg3 (unsigned)                                | 74 |

| INDEX0 RegD,Reg1,Reg2,Reg3                                                          | 74 |

| INDEX1 RegD,Reg1,Reg2,Reg3                                                          | 74 |

| INDEX2 RegD,Reg1,Reg2,Reg3                                                          | 74 |

| INDEX4 RegD,Reg1,Reg2,Reg3                                                          | 74 |

| INDEX8 RegD,Reg1,Reg2,Reg3                                                          | 75 |

| INDEX16 RegD,Reg1,Reg2,Reg3                                                         | 75 |

| INDEX24 RegD,Reg1,Reg2,Reg3                                                         | 75 |

| INDEX32 RegD,Reg1,Reg2,Reg3                                                         | 75 |

| B.EQ Reg1,Reg2,immed-16 Branch if Reg1 = Reg2; Offset is PC-relative                | 77 |

| B.NE Reg1,Reg2,immed-16 Branch if Reg1 ≠ Reg2; Offset is PC-relative                | 77 |

| B.LT Reg1,Reg2,immed-16 Branch if Reg1 < Reg2; Offset is PC-relative                | 78 |

| B.LE Reg1,Reg2,immed-16 Branch if Reg1 ≤ Reg2; Offset is PC-relative                | 78 |

| *BEQ Reg1,Reg2,address Branch if Reg1 = Reg2                                        | 79 |

| *BNE Reg1,Reg2,address Branch if Reg1 ≠ Reg2                                        | 79 |

| *BLT Reg1,Reg2,address Branch if Reg1 < Reg2                                        | 79 |

| *BLE Reg1,Reg2,address Branch if Reg1 ≤ Reg2                                        | 79 |

| *BGT Reg1,Reg2,address Branch if Reg1 > Reg2                                        | 79 |

| *BGE Reg1,Reg2,address Branch if Reg1 ≥ Reg2                                        | 79 |

| *BEQI Reg,value,address Branch if Reg = immediate value                             | 84 |

| *BNEI Reg,value,address Branch if Reg ≠ immediate value                             | 84 |

| *BLTI Reg,value,address Branch if Reg < immediate value                             | 84 |

| *BLEI Reg,value,address Branch if Reg ≤ immediate value                             | 84 |

| *BGTI Reg,value,address Branch if Reg > immediate value                             | 84 |

| *BGEI Reg,value,address Branch if Reg ≥ immediate value                             | 84 |

| *BEQZ Reg,address Branch if Reg = 0                                                 | 85 |

| *BNEZ Reg.address Branch if Reg ≠ 0                                                 | 85 |

| *BLTZ Reg,address Branch if Reg < 0, i.e., if negative                 | 85  |

|------------------------------------------------------------------------|-----|

| *BLEZ Reg,address Branch if Reg ≤ 0, i.e., if not positive             | 85  |

| *BGTZ Reg,address Branch if Reg > 0, i.e., if positive                 | 85  |

| *BGEZ Reg,address Branch if Reg ≥ 0, i.e., if not negative             | 85  |

| *BFALSE Reg,address Branch if Reg = 0, i.e., if "false"                | 85  |

| *BTRUE Reg,address Branch if Reg ≠ 0, i.e., if "true"                  | 85  |

| UPPER20 RegD,immed-20 RegD ← (immed<<16)                               | 86  |

| UPPER16 RegD,Reg1,immed-16 RegD ← (immed<<16) + Reg1                   | 86  |

| SHIFT16 RegD,Reg1,immed-16 RegD $\leftarrow$ (Reg1 + immed-16) $<<$ 16 | 87  |

| ADDPC RegD,immed-20 RegD ← PC+immed                                    | 87  |

| AUIPC RegD,immed-20 RegD $\leftarrow$ (immed<<16) + PC                 | 88  |

| JAL RegD,immed-20 RegD ← return addr; Target ← PC+offset               | 88  |

| JALR RegD,immed-16(Reg1) RegD ← return addr; Target ← offset+Reg1      | 89  |

| *CALL address Jump to address; save return addr in "lr"                | 90  |

| *CALLR Reg1 Jump to address; save return addr in "lr"                  | 90  |

| *JUMP address Jump to address                                          | 91  |

| *JR Reg1 Indirect jump, via register                                   | 92  |

| *RET <no operands=""> Return value is in link reg "lr"</no>            | 92  |

| ENTER immed-16                                                         | 93  |

| EXIT immed-16                                                          | 93  |

| LOAD.B RegD,immed-16(Reg1)                                             | 96  |

| LOAD.H RegD,immed-16(Reg1)                                             | 96  |

| LOAD.W RegD,immed-16(Reg1)                                             | 96  |

| LOAD.D RegD,immed-16(Reg1)                                             | 96  |

| STORE.B immed-16(Reg1),Reg2                                            | 96  |

| STORE.H immed-16(Reg1),Reg2                                            | 96  |

| STORE.W immed-16(Reg1),Reg2                                            | 96  |

| STORE.D immed-16(Reg1),Reg2                                            | 96  |

| *LOADB RegD,address Where address is any value                         | 99  |

| *LOADH RegD,address                                                    | 99  |

| *LOADW RegD,address                                                    | 99  |

| *LOADD RegD,address                                                    | 99  |

| *LOADB RegD,offset(Reg1) Where offset is any value                     | 99  |

| *LOADH RegD,offset(Reg1)                                               | 99  |

| *LOADW RegD,offset(Reg1)                                               | 99  |

| *LOADD RegD,offset(Reg1)                                               | 99  |

| *STOREB address,Reg2 Where address is any value                        | 101 |

| *STOREH address,Reg2                                                   | 101 |

| *STOREW address,Reg2                                                   | 101 |

| *STORED address,Reg2                                                   | 101 |

| *STOREB offset(Reg1),Reg2 Where offset is any value                    | 101 |

| *STOREH offset(Reg1),Reg2                                              | 101 |

| *STOREW offset(Reg1),Reg2                                              | 101 |

| *STORED offset(Reg1),Reg2                                              | 101 |

| CAS RegD,Reg1,Reg2,Reg3 Compare and Set                                | 102 |

| FENCE <no operands=""></no>                                            | 104 |

| ALIGNH RegD,Reg1,Reg2,Reg3 Reg3 (unaligned addr) gives shift amount             | 107 |

|---------------------------------------------------------------------------------|-----|

| ALIGNW RegD, Reg1, Reg2, Reg3 Reg3 (unaligned addr) gives shift amount          | 107 |

| ALIGND RegD,Reg1,Reg2,Reg3 Reg3 (unaligned addr) gives shift amount             | 107 |

| INJECT1H RegD,Reg1,Reg2,Reg3 RegD ← Reg1; inject Reg2 per addr in Reg3          | 112 |

| INJECT2H RegD,Reg1,Reg2,Reg3 RegD ← Reg1; inject Reg2 per addr in Reg3          | 112 |

| INJECT1W RegD,Reg1,Reg2,Reg3 RegD ← Reg1; inject Reg2 per addr in Reg3          | 112 |

| INJECT2W RegD,Reg1,Reg2,Reg3 RegD ← Reg1; inject Reg2 per addr in Reg3          | 112 |

| INJECT1D RegD,Reg1,Reg2,Reg3 RegD ← Reg1; inject Reg2 per addr in Reg3          | 112 |

| INJECT2D RegD,Reg1,Reg2,Reg3 RegD ← Reg1; inject Reg2 per addr in Reg3          | 112 |

| ILLEGAL <no operands=""></no>                                                   | 119 |

| SYSRET <no operands=""></no>                                                    | 119 |

| SLEEP1 <no operands=""> Enable interrupts; enter light sleep state</no>         | 120 |

| SLEEP2 <no operands=""> Enable interrupts; enter deep sleep state</no>          | 120 |

| RESTART <no operands=""> Same as Power-On-Reset</no>                            | 121 |

| DEBUG <no operands=""></no>                                                     | 122 |

| BREAKPOINT <no operands=""></no>                                                | 122 |

| SYSCALL immed-10                                                                | 123 |

| CONTROL RegD,Reg1,immed-16                                                      | 124 |

| CONTROLU RegD,Reg1,immed-16                                                     | 124 |

| TLBCLEAR <no operands=""> Invalidate all TLBs for current ASID</no>             | 129 |

| TLBFLUSH Reg1 Invalidate TLB for virtual address in Reg1                        | 129 |

| CHECKADDR RegD,Reg1,immed-3 Reg1 = virt addr; RegD ← except. code or 0          | 130 |

| CSRSWAP RegD,CSRReg1,Reg2 RegD ← CSR; CSR ← Reg2                                | 132 |

| CSRREAD RegD,CSRReg1 Reg1 encodes CSR; RegD ← CSR                               | 132 |

| CSRSET CSRReg1,immed-16 Set selected bits in CSR                                | 132 |

| CSRCLR CSRReg1,immed-16 Clear selected bits in CSR                              | 132 |

| *CSRWRITE CSRReg1,Reg2 Reg1 encodes CSR; CSR ← Reg2                             | 133 |

| GETSTAT RegD RegD $\leftarrow$ CSR_STATUS & 0x0000000000003f8                   | 133 |

| PUTSTAT Reg1 CSR_STATUS [9:3] ← Reg1 [9:3]                                      | 133 |

| FADD RegD,Reg1,Reg2 RegD ← Reg1 + Reg2                                          | 134 |

| FSUB RegD,Reg1,Reg2 RegD ← Reg1 - Reg2                                          | 134 |

| FMUL RegD,Reg1,Reg2 RegD ← Reg1 × Reg2                                          | 134 |

| FDIV RegD,Reg1,Reg2 RegD ← Reg1 / Reg2                                          | 134 |

| FMIN RegD,Reg1,Reg2 RegD $\leftarrow$ MIN (Reg1, Reg2)                          | 134 |

| FMAX RegD,Reg1,Reg2 RegD $\leftarrow$ MAX (Reg1, Reg2)                          | 134 |

| FNEG RegD,Reg1 RegD $\leftarrow$ -Reg1                                          | 134 |

| FABS RegD,Reg1 RegD ← ABSOLUTE_VALUE (Reg1)                                     | 134 |

| FSQRT RegD,Reg1 RegD $\leftarrow$ SQUARE_ROOT (Reg1)                            | 134 |

| FEQ RegD,Reg1,Reg2 RegD $\leftarrow$ (Reg1 = Reg2) ? 1 : 0 (float compare)      | 134 |

| FLT RegD,Reg1,Reg2 RegD $\leftarrow$ (Reg1 < Reg2) ? 1 : 0 (float compare)      | 134 |

| FLE RegD,Reg1,Reg2 RegD $\leftarrow$ (Reg1 $\leq$ Reg2) ? 1 : 0 (float compare) | 134 |

| FCVTFI RegD,Reg1 Convert: floating-point ← int                                  | 134 |

| FCVTIF RegD,Reg1 Convert: int ← floating-point                                  | 134 |

| FMADD RegD,Reg1,Reg2,Reg3 RegD ← (Reg1 × Reg2) + Reg3                           | 134 |

| FNMADD RegD,Reg1,Reg2,Reg3 RegD $\leftarrow$ (-(Reg1 × Reg2)) + Reg3             | 134 |

|----------------------------------------------------------------------------------|-----|

| FMSUB RegD,Reg1,Reg2,Reg3 RegD $\leftarrow$ (Reg1 × Reg2) - Reg3                 | 134 |

| FNMSUB RegD,Reg1,Reg2,Reg3 RegD $\leftarrow$ (-(Reg1 × Reg2)) - Reg3             | 134 |

| *FGT RegD,Reg1,Reg2 RegD $\leftarrow$ (Reg1 > Reg2) ? 1 : 0 (float compare)      | 136 |

| *FGE RegD,Reg1,Reg2 RegD $\leftarrow$ (Reg1 $\geq$ Reg2) ? 1 : 0 (float compare) | 137 |

# **Chapter 1: Introduction**

What is originality? Undetected plagiarism.

— Dean William R. Inge

# **Quick Summary**

- Blitz-64 introduces a novel 64-bit "Instruction Set Architecture" (ISA).

- The goals of the Blitz-64 project are:

- Create a complete hardware / software system

- Simple, small, easy to understand

- Fully functional and fully modern

- Reliability, security, and error handling are emphasized

- This project is open, not proprietary

- Software and documents use dates instead of version numbers

#### **Instruction Set Architectures**

An Instruction Set Architecture (ISA) defines, describes, and specifies how a particular computer processor core works. The ISA describes the registers and all the machine instructions. The ISA specifies exactly what each instruction does and how it is encoded into bits.

The ISA forms the **interface between hardware and software**. Hardware engineers design digital circuits to implement a given ISA and software engineers write code (operating systems, compilers, etc.) based on a given ISA specification.

There are a number of Instruction Set Architectures in widespread use, for example:

x86-64 (AMD, Intel) ARM (ARM Holdings) SPARC (Sun/Oracle) RISC-V (Berkeley/open source)

Most of these ISAs are **proprietary** and very complex. The **details are obscured** in lengthy manuals and some details of the ISA are not made public at all. Furthermore, the widely used ISAs have been around for years and their designs carry baggage as a result, e.g., for **backward compatibility**. Since these **legacy designs** were first created, we've learned more about how to design computers. Changes in silicon hardware technology have also had an impact on which design choices are now optimal. The RISC-V project attempts to address the issues of open source and interoperability, and heavily influences Blitz-64.

In this document we define and describe a new ISA called Blitz-64.

## **Goals and Principles: Personal Statements**

The following are the guiding goals of the Blitz-64 architecture.

- Simple, small, modest

- Understandable

- Reliable

- Good error reporting/recovery

- Secure against malware

- No desire to support virtualization / hypervisors (due to security concerns)

- Programmable, pleasing design

- Encourage assembly language and kernel programming and experimentation

All modern processor cores have become far too complex for any single individual to understand. My primary goal is to create a computer that is **simple** enough for one person to understand, yet fully modern and practical.

The way I hope to achieve simplicity is to design the entire system (the ISA, all the system software, and good documentation) alone, myself. The resulting system must, by necessity, be radically simpler than existing computers. A key aspect to

making any design simpler is to make it smaller. Size and complexity are strongly correlated. A system designed by one person must be **fairly small and modest** and, as a result, it will necessarily be simpler and easier to understand.

On the hardware side, modern computer cores (ARM, x86-64, etc.) are just too complicated to be understood by any single human being. They are designed by vast teams of specialists; they incorporate legacy designs; their documentation comprises thousand of pages, and they are proprietary and at least partially shrouded in corporate secrecy.

On the software side, modern operating systems contain millions of lines of code written over the course of many decades, by vast numbers of programmers. Much of the code is written in "C", which is notoriously difficult to read, modify, and validate. This is unquestionably true of Apple, Windows, and Linux software. Nobody can fully comprehend a million lines of code; these large chunks of software must remain mysterious black boxes. So instead, programmers today blindly trust and build on top of a gigantic accumulation incompletely understood software. It's remarkable that today's software works as well as it does.

It is easier to use, trust, and rely on systems that we understand. A primary goal of Blitz-64 is to create a complete, modern, and functional computer ISA and collection of system software that is **understandable** by a single person.

<u>Elegance of design</u> is always a laudable goal. Elegance and beauty are correlated with simplicity and size. By keeping the design simple and small, I believe that elegance of design will follow.

As computers are growing more complex and integrated into society, reliability is becoming ever more critical. The more complex a system is, the more difficult it is to verify correctness and repair bugs. Making systems simpler contributes to greater reliability. But beyond simplicity, many small design decisions along the way determine whether **performance execution speed** or **reliability** is preferred and optimized.

To increase reliability, more error checking must be done at runtime. Furthermore, when errors occur, they must be handled with more care, better reporting, and reasonable recovery. Error checking incurs a performance penalty. Modern systems evolved from ancient, slow computers where performance was the critical bottleneck. The legacy systems, upon which the foundation of all modern software is built, often ignored the possibility of program bugs and focused all effort on

execution speed. Back in the day, when program size was measured in tens or hundreds of lines of code, this was a reasonable choice.

The dynamic has obviously shifted, changing the tradeoff analysis. Today's computers are really fast. It may now be the case that performance is being hurt by complexity itself. As the size and complexity of software grows, the reliability of individual parts and components becomes ever more critical. (For example, a failure rate of 0.1% for each part might be acceptable for a system with 100 parts, but is totally unacceptable with a million parts.)

I recognize that performance is very, very important, but I reject the "performance at all costs" mentality. One of my goals is to perform **greater runtime error checking** and **improved error recovery**, even at the cost of performance. The radical choice I make is to sacrifice performance for increased reliability, whenever there is a choice.

As an example, the Blitz-64 architecture specifies overflow detection and exception processing on standard arithmetic computations, like the ADD instruction. In the "C" language, an overflow results in no error processing and the program proceeds using incorrect values. In other words, the program fails silently. For any program that has not undergone a thorough numerical analysis (in other words, almost every program), this approach is abominable.

Simplicity also impacts physical reliability. In order to increase the reliability of computer circuits in the face of physical insults (e.g., radiation, temperature extremes, and other environmental problems) simplicity of the ISA has several benefits. First, simpler designs can be implemented with fewer transistors. Given a fixed die size, this allows the individual transistors and wires to be made physically larger. Bigger transistors are more fault tolerant, which increases the circuit's reliability. Second, the small size of an implementation allows more space for redundancy, and duplication is another important approach to fault tolerance. A simple computer with a small footprint can be replicated several times to increase reliability.

Modern computer systems are increasingly susceptible to malware, intrusion, and hacking. In addition to guarding against physical insults, the threats of intentional attack require careful attention in ISA designs.

The approach with current systems seems to be the "whack-a-mole" strategy: when a security hole is uncovered, the hole is patched. Then, wait and repeat. With a

gigantic body of legacy software — millions of lines of code, which nobody really understands — the "whack-a-mole" approach seems to be the only viable strategy.

My approach to <u>increased security</u> includes creating a smaller, simpler design, improving error detection, and assuming the presence of "black hat" players (bad guys) in all domains, at all times.

The goal of creating software that is secure, reliable, and bug-free is obviously both worthy and elusive. A key approach to making a system secure is to make it reliable and bug-free. So my focus on simplicity and reliability is, implicitly, a focus on security.

In order to verify a computer system, to find and patch security holes, it is necessary to thoroughly review and analyze the system design. With complex ISAs and millions of lines of code, the task of verification is problematic. Simplicity and smallness help a lot.

Another security threat involves embedding spyware or malware within system software. Such software remains present during normal operation and can act as a backdoor for black hat access to private data at any time. Embedded backdoor software can also perform secret surveillance of behavior and activity on the computer, compromising the trust and security of the system.

Spyware can be injected into the system software at many levels. My approach to shutting out spyware and embedded malware involves:

- Designing and implementing all the software from scratch

- Completely reimplementing the boot process

- Banning dynamically alterable firmware

- Securely controlling kernel updates

- Keeping the software small enough that it can be entirely reviewed

- Performing system design and implementation in a sort of clean-room isolation

In particular, **hypervisors** and emulated systems are considered to be a threat to security. It is difficult for kernel software to be certain that it is running on a bare machine, but it is critical to security. For example, a kernel is intended to prevent security leaks, but if that kernel is being emulated or run in a hypervisor context, all the actions of the kernel are subject to surveillance and manipulation.

There is currently a trend toward increased use of hypervisors. Typically, a user wants to own a single computer, but be able to run software developed for the Mac, Windows, Linux, etc. operating systems. The clever approach is to run multiple operating systems on top of hypervisor software. As a result, modern ISAs are designed with an eye to supporting hypervisor-like software, to make the hosted OSes run faster.

The Blitz-64 system takes the opposite approach. While there seems to be little we can do to prevent software from being executed in an emulated environment, the emulation of kernels should be discouraged due to security issues. The Blitz-64 architecture makes no concessions and no special instructions are added to support the emulation of "kernel mode" software. This is an intentional design decision, not an oversight.

A final goal of the Blitz-64 project is to **support programming for fun** and, in particular, to support assembly language and kernel programming.

Programming on "bare metal" is an acquired taste and certainly does not appeal to the mass of average programmers because of the high level of skill and attention to detail it requires. But there may be a small group of highly proficient hobbyists who want this experience.

I feel that modern computers are simply too complex for programming to be fun. Kernel programming is pretty much impossible. I want to create a computer system that is more than a one-off, home-brew computer. My goal is to design a computer that is small and simple, yet roughly as functional as an ARM or x86-64 machine. Basically, I want to create a computer that programmers will enjoy — that I will enjoy programming.

## **Document Revision History / Permission to Copy**

Version numbers are not used to identify revisions to this document. Instead the date and the author's name are used. The document history is:

| <u>Date</u>     | <u>Author</u>                                                           |

|-----------------|-------------------------------------------------------------------------|

| 23 May 2018     | Harry H. Porter III <i><initial version=""></initial></i>               |

| 28 May 2019     | Harry H. Porter III <i><document completed="" mostly=""></document></i> |

| 24 May 2021     | Harry H. Porter III < new instructions added>                           |

| 18 October 2022 | Harry H. Porter III <i><version 2.0="" isa="" of=""></version></i>      |

| 23 April 2023   | Harry H. Porter III <i><changes csr_pgtable="" to=""></changes></i>     |

For details, consult the appendix titled "Recent Changes".

In the spirit of the open-source and free software movements, the author grants permission to freely copy and/or modify this document, with the following requirement:

You must not alter this section, except to add to the revision history. You must append your date/name to the revision history.

Any material lifted should be referenced.

#### **Relevant Software Tools**

The primary software tools relevant to this document are:

- The Blitz-64 <u>virtual machine</u> a "C" program called "blitz"

- The Blitz-64 <u>assembler</u> a "C" program called "asm"

- The Blitz-64 <u>linker</u> a "C" program called "link"

For our purposes, the terms "emulator" and "virtual machine" are synonymous.

| <u>Tool</u> | <u>Version Described Here</u>  | Coding Status |

|-------------|--------------------------------|---------------|

| blitz       | < same date as this document > | Completed     |

| asm         | < same date as this document > | Completed     |

link

< same date as this document >

Completed

Instead of version numbers, the Blitz-64 project uses dates to identify versions of both programs and documents. By comparing dates, you can determine whether this document matches the version of the tools you are using or, if not, which is more recent.

# **Chapter 2: Terminology and Notation**

If you can't convince them, confuse them.

— Harry S Truman

# **Quick Summary**

- "Halfword" = 16 bits = 2 bytes.

- "Word" = 32 bits = 4 bytes.

- "Doubleword" = 64 bits = 8 bytes.

- Main memory is byte addressable.

- Main memory is Big Endian.

- The notation [n:m] is used to identify bits.

- For example, [63:60] means the most significant (MSB) 4 bits in a doubleword.

- We use KiByte, MiByte, GiByte... instead of KByte, MByte, GByte...

- Alignment (e.g., halfword, word, doubleword) is defined.

- Proper alignment for sizes 8, 16, 32, and 64 bits is defined.

- Properly aligned doublewords are at addresses divisible by 8 (ending in bits 000).

- Integers are represented with signed, two's complement values.

- All arithmetic is done using 64 bits.

- Sign-extension enlarges an integer represented in signed two's complement binary.

- Size reduction (e.g., from 64 to 32 bits) may result in an "overflow" error.

#### **Kilo and Mega Prefixes**

There has been some confusion in computer science documentation regarding abbreviations for large numbers. For example:

We use the following prefix notation for large numbers, which is becoming common in the context of computer architecture:

| Pı | <u>refix</u> | <u>Example</u> | <u>Valu</u>            | <u>e</u>                |                          |

|----|--------------|----------------|------------------------|-------------------------|--------------------------|

| Ki | kibi         | KiByte         | $2^{10}$               | 1,024                   | <b>~</b> 10³             |

| Mi | mebi         | MiByte         | $2^{20}$               | 1,048,576               | <b>~</b> 10 <sup>6</sup> |

| Gi | gibi         | GiByte         | <b>2</b> <sup>30</sup> | 1,073,741,824           | $\sim 10^{9}$            |

| Ti | tebi         | TiByte         | $2^{40}$               | 1,099,511,627,776       | $\sim 10^{12}$           |

| Pi | pebi         | PiByte         | $2^{50}$               | 1,125,899,906,842,624   | $\sim 10^{15}$           |

| Ei | exbi         | EiByte         | $2^{60}$               | 1,152,921,504,606,846,9 | $76 \sim 10^{18}$        |

Contrast this to the standard metric prefixes, which we avoid:

| <u>Prefix</u> |      | <b>Example</b> | <u>Value</u> |                           |  |

|---------------|------|----------------|--------------|---------------------------|--|

| K             | kilo | KByte          | $10^{3}$     | 1,000                     |  |

| M             | mega | MByte          | $10^{6}$     | 1,000,000                 |  |

| G             | giga | GByte          | $10^{9}$     | 1,000,000,000             |  |

| T             | tera | TByte          | $10^{12}$    | 1,000,000,000,000         |  |

| P             | peta | PByte          | $10^{15}$    | 1,000,000,000,000,000     |  |

| E             | exa  | EByte          | $10^{18}$    | 1,000,000,000,000,000,000 |  |

# **Bits and Bytes**

We use the terms "byte", "halfword", "word", and "doubleword", to refer to various sizes of binary data.

|            | number<br><u>of bytes</u> | number<br><u>of bits</u> | example value (in hex) |

|------------|---------------------------|--------------------------|------------------------|

| byte       | 1                         | 8                        | A4                     |

| halfword   | 2                         | 16                       | C4F9                   |

| word       | 4                         | 32                       | AB12CD34               |

| doubleword | 8                         | 64                       | 0123456789ABCDEF       |

A single hex digit can be used to represent 4 bits:

| <u>Binary</u> | <u>Hex</u> |

|---------------|------------|

| 0000          | 0          |

| 0001          | 1          |

| 0010          | 2          |

| 0011          | 3          |

| 0100          | 4          |

| 0101          | 5          |

| 0110          | 6          |

| 0111          | 7          |

| 1000          | 8          |

| 1001          | 9          |

| 1010          | Α          |

| 1011          | В          |

| 1100          | C          |

| 1101          | D          |

| 1110          | E          |

| 1111          | F          |

|               |            |

The 8 bits within a byte are conveniently expressed with two hex digits. For example:

| <u>8 bit</u> | <u>byte</u> | <u>In Hex</u> |

|--------------|-------------|---------------|

| 1010         | 0100        | A4            |

The 32 bits in a word are given with 8 hex digits. For example:

|           | <u>In Hex</u> |           |           |          |

|-----------|---------------|-----------|-----------|----------|

| 1010 1011 | 0001 0010     | 1100 1101 | 0011 0100 | AB12CD34 |

Sometimes we insert spaces or commas to make long hex values more readable.

These examples show different ways of representing the same doubleword:

0123456789ABCDEF 0123\_4567\_89AB\_CDEF 0123,4567,89AB,CDEF 0123 4567 89AB CDEF 01234567 89ABCDEF

Often we prefix hex values with "0x" to make it clear they are hex values and not decimal:

0x1234

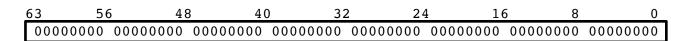

The bits within an 8-bit byte are numbered from 0 (lower, least significant) to 7 (upper, most significant).

| _ 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|---|---|---|---|---|---|---|

| 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

The bits within a 16 bit halfword are numbered from 0 to 15.

The bits within a 32 bit word are numbered from 0 to 31.

The bits within a 64 bit doubleword are numbered from 0 to 63.

We use the following notation to represent a range of bits:

| <u>Example</u> | <u>Meaning</u>                 |

|----------------|--------------------------------|

| [7:0]          | All bits in a byte             |

| [63:0]         | All bits in a doubleword       |

| [31:28]        | The upper 4 bits in a word     |

| [5]            | The 6th bit from the right end |

|                |                                |

# **Main Memory**

Main memory is byte addressable.

Main addresses are 36 bits. We generally express addresses in hex. Here are two equivalent notations we use:

Memory can be viewed as a sequence of bytes:

| address         | data            |  |  |

|-----------------|-----------------|--|--|

| <u>(in hex)</u> | <u>(in hex)</u> |  |  |

| 0_0000_0000     | 89              |  |  |

| 0_0000_0001     | AB              |  |  |

| 0_0000_0002     | CD              |  |  |

| 0_0000_0003     | EF              |  |  |

| 0_0000_0004     | 01              |  |  |

| 0_0000_0005     | 23              |  |  |

| 0_0000_0006     | 45              |  |  |

| 0_0000_0007     | 67              |  |  |

| • • •           | • • •           |  |  |

| F_FFFF_FFFC     | E0              |  |  |

| F_FFFF_FFFD     | E1              |  |  |

| F_FFFF_FFFE     | E2              |  |  |

| F_FFFF_FFFF     | E3              |  |  |

<sup>&</sup>quot;Low" memory refers to smaller addresses, closer to 0\_0000\_0000. "High" addresses are numerically greater.

### **Big Endian**

Blitz-64 is a big endian architecture.

As an example, assume that main memory holds the following bytes:

| address<br>(in hex) | data<br><u>(in hex)</u> |

|---------------------|-------------------------|

| • • •               | • • •                   |

| E_5000_0004         | 1A                      |

| E_5000_0005         | 2B                      |

| E_5000_0006         | 3C                      |

| E_5000_0007         | 4 D                     |

| E_5000_0008         | 5E                      |

| E_5000_0009         | 6F                      |

| E_5000_000A         | 70                      |

| E_5000_000B         | 81                      |

| E_5000_000C         | 92                      |

| E_5000_000D         | A3                      |

| E_5000_000E         | B4                      |

| E_5000_000F         | C5                      |

| • • •               | • • •                   |

In Blitz-64, the registers are 64 bits (8 bytes) wide. There are several LOAD and STORE instructions, which can move either a byte, halfword, word or doubleword between memory and a register.

Consider a LOADB instruction that loads a byte from address 0xE\_5000\_0004. After execution, the register will contain:

$$0 \times 0000 \_ 0000 \_ 0000 \_ 001A$$

Consider a LOADW instruction which loads a word from address 0xE\_5000\_0004. After execution, the register will contain:

**Commentary** In a little endian architecture, the order of the bytes is changed whenever data is copied from memory to a register or stored from a register into memory. This can be a source of confusion, particularly when humans look at a printout of memory contents.

As an example, consider this memory:

| address<br>(in hex) | data<br>(in hex) |

|---------------------|------------------|

| • • •               | • • •            |

| E_5000_0004         | 1A               |

| E_5000_0005         | 2B               |

| E_5000_0006         | 3C               |

| E_5000_0007         | 4D               |

| E_5000_0008         | 5E               |

| E_5000_0009         | 6F               |

| E_5000_000A         | 70               |

| E_5000_000B         | 81               |

| E_5000_000C         | 92               |

| E_5000_000D         | A3               |

| E_5000_000E         | В4               |

| E_5000_000F         | C5               |

| • • •               | • • •            |

Memory can be viewed either as a series of bytes, or as a series of larger units, such as words or doublewords.

With a "big endian" computer, this memory is interpreted as:

| address<br>(in hex) | data<br><u>(in hex)</u> |  |

|---------------------|-------------------------|--|

| • • •               | • • •                   |  |

| E_5000_0004         | 1A2B3C4D                |  |

| E_5000_0008         | 5E6F7081                |  |

| E_5000_000C         | 92A3B4C5                |  |

| • • •               | • • •                   |  |

With a "little endian" computer, this memory is interpreted as:

| address<br>(in hex) | data<br><u>(in hex)</u> |  |

|---------------------|-------------------------|--|

| • • •               | • • •                   |  |

| E_5000_0004         | 4D3C2B1A                |  |

| E_5000_0008         | 81706F5E                |  |

| E_5000_000C         | C5B4A392                |  |

| • • •               | • • •                   |  |

Big endian architectures are simpler to understand since the bytes are not reordered during loads and stores.

The primary argument for choosing little endian is legacy compatibility. The two approaches are similar in terms of circuit complexity.

# **Alignment**

A "halfword aligned" address is an address that is a multiple of 2. The last bit of a halfword-aligned address will always be 0. Likewise, a "word aligned" address is a multiple of 4, and ends with the bits 00. And finally, a "doubleword aligned" address will be evenly divisible by 8 and will end with bits 000.

A halfword-sized value is said to be "**properly aligned**" if it is stored at a halfword aligned address. Likewise, a word-sized value is properly aligned if it is stored at a word aligned address. And similarly, a doubleword-sized value is properly aligned if it is stored at a doubleword aligned address.

Blitz-64 requires data to be properly aligned for the LOAD and STORE instructions.

Full-sized instructions are 32 bits in length. Compressed instructions are 16 bits in length. All instructions are required to be halfword aligned. The LSBit of the PC is hardwired to 0, so there can be never be an exception when an instruction is fetched. When the PC is loaded — for example during a BRANCH or CALL instruction — the LSBit is simply ignored; no exception will be generated.

<u>Commentary</u> BRANCH and CALL instructions are normally generated by a compiler or assembler, which will always place the target instruction on a properly aligned address. Therefore, there is little possibility that an error will be made.

However, with LOADs and STOREs, the address may come from a programmer computed pointer, which may easily be in error. Rather than silently ignoring the last 1, 2, or 3 bits and loading/storing from an incorrect location, an "Unaligned LOAD/STORE Exception" will be signaled.

# **Signed Numbers**

Integers are represented in binary.

With **unsigned number** representation, only zero and positive integers can be represented. The maximum possible value is determined by the number of bits available and is always 2<sup>N</sup>-1, where N is the number of bits.

|            | Size           |                                                                 |

|------------|----------------|-----------------------------------------------------------------|

|            | <u>in bits</u> | Range of values                                                 |

| byte       | 8              | 0 255                                                           |

| halfword   | 16             | 0 65,535                                                        |

| word       | 32             | 0 4,294,967,295                                                 |

| doubleword | 64             | $0 \dots 18,446,744,073,709,551,615 (\approx 2 \times 10^{19})$ |

**Signed numbers** are represented using "**two's complement**" representation. The most significant bit gives the sign (1=negative; 0=zero or positive).

|           | Size    |                                                      |

|-----------|---------|------------------------------------------------------|

| _         | in bits | Range of values                                      |

| byte      | 8       | -128 127                                             |

| halfword  | 16      | -32,768 32,767                                       |

| word      | 32      | -2,147,483,648 2,147,483,647                         |

| doublewor | d 64    | -9,223,372,036,854,775,808 9,223,372,036,854,775,807 |

| To make things | simpler, we | define the | following | constants:       |

|----------------|-------------|------------|-----------|------------------|

|                | 0p-0-,      |            |           | 0 0 110 0011100. |

| <u>Name</u>     | Decimal                    | <u>Hex (64 bits)</u> |

|-----------------|----------------------------|----------------------|

| MIN_8           | -128                       | FFFF_FFFF_FFFF_FF80  |

| MAX_8           | 127                        | 0000_0000_0000_007F  |

| MAX_UNSIGNED_8  | 255                        | 0000_0000_0000_00FF  |

| MIN_16          | -32,768                    | FFFF_FFFF_FFFF_8000  |

| MAX_16          | 32,767                     | 0000_0000_0000_7FFF  |

| MAX_UNSIGNED_16 | 65,535                     | 0000_0000_0000_FFFF  |

| MIN_32          | -2,147,483,648             | FFFF_FFFF_8000_0000  |

| MAX_32          | 2,147,483,647              | 0000_0000_7FFF_FFFF  |

| MAX_UNSIGNED_32 | 4,294,967,295              | 0000_0000_FFFF_FFFF  |

| MIN_64          | -9,223,372,036,854,775,808 | 8000_0000_0000_0000  |

| MAX_64          | 9,223,372,036,854,775,807  | 7FFF_FFFF_FFFF_FFFF  |

|                 |                            |                      |

The Blitz-64 architecture relies entirely on 64 bit signed integers. There is only one type for integers.

Arithmetic on 32 bit quantities is not supported, although there are instructions to enlarge and shrink values between 8, 16, 32, and 64 bits.

Note that the range of signed doublewords is sufficient to represent every *byte*, *halfword*, and *word* value regardless of whether it is *signed* or *unsigned*.

**Commentary** Signed 64 bit integers seem both necessary and sufficient for computer arithmetic. There seems to be no good reason to include support for "unsigned 64 bit integer" operations.

The range of signed doublewords is adequate for expressing quantities such as an "astronomical unit" in microns, the number of seconds since the big bang, or the world GDP in hundredths of a cent. Unfortunately, the range of 32 bit words is inadequate for many things, such as counting humans, the US federal debt in dollars, the number milliseconds since January 1, 1970 (widely used by computers), or the number of bytes of main memory in typical smartphones. Any programmer who uses 32 bit integers needs to think very, very carefully about overflow conditions.

The use of unsigned data types made sense in the past, when the word sizes were smaller. In some applications, the difference between a maximum value of 127 and 255 (for byte-sized data), or between 32,767 and 65,535 (for 16 bit data) was important and critical, and worth sacrificing the ability to represent negative values.

It is even conceivable that some applications needed numbers between 2,147,483,647 and 4,294,967 295 (for 32-bit data), while at the same time, never needing negative values.

However, it's virtually impossible to imagine an application for which unsigned 64 bit numbers are appropriate. For such an application, the expected values would be expected to exceed 9,223,372,036,854,775,807, and yet be guaranteed to never exceed 18,446,744,073,709,551,615, and also be guaranteed to never be negative!

**Commentary** The cost of using "unsigned" binary numbers is that negative values must be thrown out. Negative numbers are obviously useful and shouldn't be ignored or excluded. Throwing out the negative numbers is a bad, anti-mathematical idea. It's dangerous because we know it causes all sorts of program bugs; it makes the discrepancy between "computer integers" and "mathematical integers" vastly greater; and a proliferation of different datatypes complicates programming.

In Blitz-64, if the programmer wishes to force some number into one of the limited, legacy ranges, he/she can easily write tests such as:

```

if (x<0 || x>MAX_UNSIGNED_32) ...

```

**Commentary** In any core processor, the speed of addition is critical since addition is involved in:

- Incrementing the PC.

- Performing address calculations in LOAD, STORE, BRANCH, ... instructions.

- Implementing the ADD and SUB instructions, for loop control, arrays, etc.

The Blitz-64 architecture does not support arithmetic on integer data of size byte, halfword, or word. How much of a performance penalty does this radical decision incur?

In modern cores, we can assume that addition is implemented with carry lookahead units (CLA), each with 4 inputs. Thus, the carry lookahead tree has a branching factor of 4 and the depth of the tree determines the gate delay for the adder unit. A 16 bit adder will require 2 CLA levels  $(4 \times 4)$  to add 16 bits. A 32 bit adder will require 3 levels, since  $4 \times 4$  is not enough. However, a 3 level tree will also be sufficient for a 64 bit adder, since  $4 \times 4 \times 4 = 64$ .

Therefore, **64-bit addition incurs no performance penalty** over 32 bit addition. This holds for subtraction, as well.

Concerning multiplication, the execution time is constrained by the time to add a column of numbers. The setup and sign-adjustment logic incurs a constant delay which does not depend on word size.

For 32 bit multiplication, a set of 32 numbers must be added. For a 64 bit multiplication, a set of 64 numbers must be added. Many of the additions can be done in parallel, and the final result sum can be determined in log time. A set of 32 numbers can be added using a tree of adders of depth 5. A set of 64 numbers can be added using a tree of adders of depth 6. Therefore, the time required **to multiply 64 bit values** will be **no more than 20% greater** than the time required to multiply 32 bit values.

Thus, our (perhaps counterintuitive) **conclusions** are:

- There is no significant performance penalty to pay for performing all arithmetic using 64 bits.

- The simplicity to be gained by eliminating legacy data types (i.e., "unsigned", "byte", "halfword", and "word") is well worth any small performance cost.

#### **Sign-Extension**

A value of one size can be "sign-extended" to a larger size. For example, a 32 bit word can be sign-extended to 64 bits.

The sign-extension operation does not change the integer value of the number.

The sign-extension operation looks at the sign bit (i.e., the most significant bit) of the smaller number. Then, that bit value is replicated as necessary to fill additional bits on the left, most significant end of the smaller value, until it is the required larger size.

For example, sign-extending a 16 bit value to 64 bits will look at bit [15] of the input value. If it is "1", the number is negative. To sign-extend it to 64 bits, the uppermost 48 bits, i.e., bits [63:16], will be filled with "1". Otherwise, the uppermost bits will be filled with "0".

Many Blitz-64 instructions include a 16 bit "immediate" value, which is encoded directly within the instruction. This immediate value is sign-extended to 64 bits before being used.

#### **Size Reduction**

Often it is necessary to take a larger value and reduce its size. For example, a register may contain a doubleword value (i.e., 64 bits) and we may want to reduce it to a halfword (i.e., 16 bits).

A size reduction can be performed by simply cutting off (i.e., ignoring, eliminating) the uppermost bits.

If the original value happens to lie within the range representable by the smaller size, then there is no problem. The value remains unchanged by the operation.

If the original value does not lie within the range representable by the smaller size, then the new value will be numerically different. This is considered a form of "overflow", in the sense that the operation has resulted in a mathematically incorrect result.

Looking at a value, we can easily determine whether a size reduction will result in overflow or not. For example, if we are reducing a 64 bit value to 16 bits, we ask whether the upper 48 bits (i.e., bits [63:16]), which will be discarded, are all equal to the sign bit (i.e., bit [15]) of the new, smaller result. If so, there is no problem. In other words, we ask whether bits [63:15] are either all 0s or all 1s. If the uppermost 49 bits are all equal, there is no problem, but if both 0s and 1as are present, the size reduction operations will cause an overflow error.

# **Chapter 3: Architectural Summary**

A doctor can bury his mistakes but an architect can only advise his clients to plant trees.

— Frank Lloyd Wright

# **Quick Summary**

- Register size: 64 bits.

- Number of general purpose registers: 16.

- Zero register: r0 always reads as zero and acts as a destination for unneeded results.

- All remaining registers (r1, r2, ... r15) are general purpose and equally functional.

- Natural data size: 64 bits (i.e., doubleword)

- Integer overflow is never ignored; an exception is always generated.

- All arithmetic is done using 64 bit signed integers.

- Floating Point:

- No separate floating-point regs. General purpose regs are used.

- Floating point precision: Double only; there is no single precision.

- Main memory is Big Endian.

- Instructions are 32 bits in size.

- Compressed instructions are multiples of 8 bits in size.

- Number of privilege modes: 2 (Kernel and User).

- Number of Control and Status Registers (CSRs): 16.

- Size of Control and Status Registers (CSRs): 64 bits.

- Program-generated addresses: 36 bits.

- Maximum Physical Memory: 16 GiBytes.

- Memory-Mapped Address Range: 16 GiBytes.

- Maximum Virtual Address Space: 32 GiBytes.

- Page size: 16 KiBytes.

- Virtual Memory System: Page tables are supported.

# Memory, Addresses, and Memory-Mapped I/O

The maximum physical memory is 16 GiBytes.

There is an additional 16 GiBytes of physical address space allocated for memory-mapped I/O.

Physical addresses (for physical memory and memory-mapped I/O) are 35 bit addresses. Note that  $2^{35} = 32$  Gi.

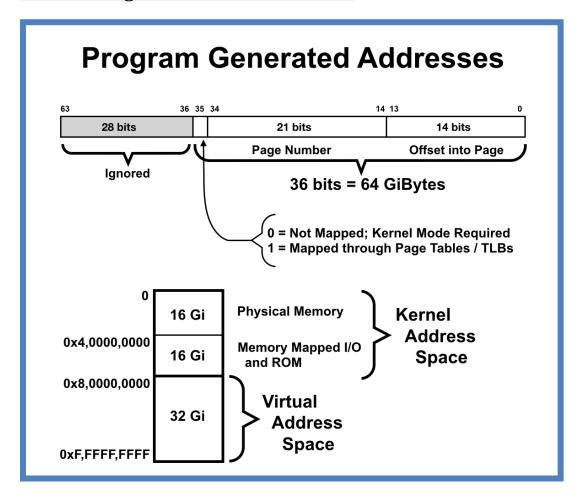

All program-generated addresses are 36 bits.

The maximum address space size is 64 Gi. Note that  $2^{36}$  = 64 Gi.

#### **Supporting Larger Main Memory**

Using virtual memory and page tables, up to **16 TiBytes of physical memory** is supported.

In the basic configuration, up to 16 GiBytes of physical memory is supported in a simple, uniform, linear address space. This should suffice for many applications. Larger memory sizes can be supported, but these can only be accessed via virtual addresses and the page table mapping.

Virtual memory and the memory mapping scheme are discussed in a later chapter.

The limitation on addresses to 36 bits might seem naïve and overly restrictive, but this is an important design choice and was not made lightly. ISA design involves a trade-off between (1) a large number of registers, (2) a small instruction size, (3) long addresses, and (4) the number of instructions required to load arbitrary addresses. Since you can't have it all, our design decisions involve a compromise on these issues.

Remember that main memory is only one tier in a memory hierarchy ranging from terabytes of solid state stable memory to megabytes of fast cache. Main memory is properly viewed as a staging ground in which programs and data are held, in order to supply the core with grist for computation. It is nothing more than a form of percore cache between a processing unit and shared data sources. We predict that the bandwidth between main memory and the core/ fast-cache circuitry will remain a

performance bottleneck; 16 GiBytes seems more than adequate to keep a single core busy. Since Blitz-64 cores may be deployed in multicore systems with 100s or 1000s of cores, the per-core limit of 16 GiBytes is properly understood as imposing a limitation on the entire core array measured in terabytes or exabytes.

#### **The Processor State**

The entire state of a running Blitz-64 core consists of:

- The general purpose registers (r0, ... r15)

- The Program Counter (PC)

- A set of 16 "Control and Status Registers" (CSRs)

( Here we mean the directly visible state of the core, observable by software; additional state, such as related to pipeline stages, cache contents, etc. should not affect software functionality or correctness. )

## **The Registers**

The **general purpose registers** are 64 bits (a doubleword, 8 bytes) in width.

There are **16 registers**.

The registers are named **r0**, **r1**, **r2**, ... **r15**.

**Register r0** is a special "**zero register**". When read, its value is always  $0x0000_0000_0000_0000$ . Whenever there is an attempt to write to r0, the data is simply discarded.

All other registers are treated identically by the ISA; there is nothing special about any register.

By convention, several registers have special functions and these registers are given alternate names. The assembler will accept either name.

|     | Alternate   |                                         |

|-----|-------------|-----------------------------------------|

|     | <u>Name</u> | <b>Function</b>                         |

| r0  |             | Zero                                    |

| r1  |             | Argument 1 / Return Value               |

| r2  |             | Argument 2                              |

| r3  |             | Argument 3                              |

| r4  |             | Argument 4                              |

| r5  |             | Argument 5                              |

| r6  |             | Argument 6                              |

| r7  |             | Argument 7                              |

| r8  | t           | Temp register, used by assembler/linker |

| r9  | s0          | Work reg (caller-saved)                 |

| r10 | s1          | Work reg (caller-saved)                 |

| r11 | s2          | Work reg (caller-saved)                 |

| r12 | tp          | Thread data pointer                     |

| r13 | gp          | Global data pointer                     |

| r14 | lr          | Link register                           |

| r15 | sp          | Stack pointer                           |

All registers are treated equally by the ISA, with the exception of **r0**. Their special functions arise solely in how the programmer uses them in instructions.

#### **Register Usage Conventions**

The registers **r1** ... **r7** are used to pass arguments to functions and methods and **r1** is used to return results. Registers r1 ... r7 are also used as general working registers to hold local variables and intermediate results within a function or method. The compiler or assembly language programmer is free to use them as desired within functions or methods. If fewer than 7 arguments are passed, then the remaining registers can be used as general work registers in the function/method. If more than 7 arguments are passed, or if any argument is larger than a doubleword, then those arguments will be passed on the stack. If most of the registers are taken up with argument passing and the function/method has immediate need for some temporary work registers, then the function/method may, at its discretion, immediately upon entry, store the less urgently needed arguments in the stack frame, thereby freeing up registers for other uses.

The Blitz-64 calling convention sets aside a fairly large number of registers for argument passing. Each argument must be collected by the calling code and moved into a known, agreed-upon location by the caller's code. Even if the argument were

to be placed on the stack, the caller would at least need to move the argument into a register temporarily to do this.

When the compiler is compiling a function, it cannot know whether it is best for the value to be placed in a register or written to the stack. Only the called function can make an informed decision about this. Therefore, the Blitz convention is to place a large number of arguments (up to 7) in registers and let the called function store some of all of them to memory, at its discretion. Ideally, the called function can avoid moving any arguments to memory.

We considered allocating all available registers to carry arguments, but there are rarely functions with more than 7 arguments and it may be convenient for a function to have some registers free upon entry. We can assume a function with more than 7 arguments is big and complex; having three work registers available may allow the function to achieve much of its task without having to spill registers to the stack frame just to have some work registers to work with. Placing all arguments in registers and therefore leaving no work registers available means that some spills must occur immediately upon entry into the function.

Therefore, we allocate three additional registers called s0, s1, and s2 (i.e., r9, r10, and r11) as work registers.

The "**temporary register**" (register **t**, i.e., **r8**) is used by the assembler for some synthetic instructions. When describing the synthetic instructions, this document indicates whether and how register t will be used. The use of register t is "clandestine", in the sense that t is not explicitly named in the synthetic instructions. The programmer and compiler are free to use register t in a function/method, as long as they realize that some synthetic instructions may alter t.

The "caller" of a function/method should assume that registers r1...r7, t, and s0...s2 will trashed (i.e., altered or arbitrarily modified) by the "called" function/method. If the contents are important, the caller should save their contents before calling the function/method. In that sense, r1...r7, t, and s0...s2 are said to be "caller-saved".

A "callee-saved" register is one in which the caller can assume that the called function will not modify the value. Or more accurately, if the called function needs to use a callee-saved register, it will save it first and then restore it before returning.

In some sense, the registers tp, gp, and sp are callee-saved, since the convention states that they are to have the same value upon return that they had before the call.

We considered setting aside some registers as "callee-saved".1

In a program with multiple threads, each thread may have a block of data specific to that thread. The "**thread pointer register**" (register **tp**, i.e., **r12**) points to this block of data, making it easy for the thread to access its private data. Typically, this register does not change and stays constant during the entire life of the thread.<sup>2</sup>

The "**global pointer register**" (register **gp**, i.e., **r13**) points to a block of memory containing static global variables shared by all functions/methods in all threads, making it easy for the code to access these variables with a single LOAD/STORE instruction using a small offset. The 16 bit immediate offset in LOAD/STORE instructions makes it easy to access data within a 4 page (i.e., 64 KiByte) range by using offsets up to ±32 KiBytes.

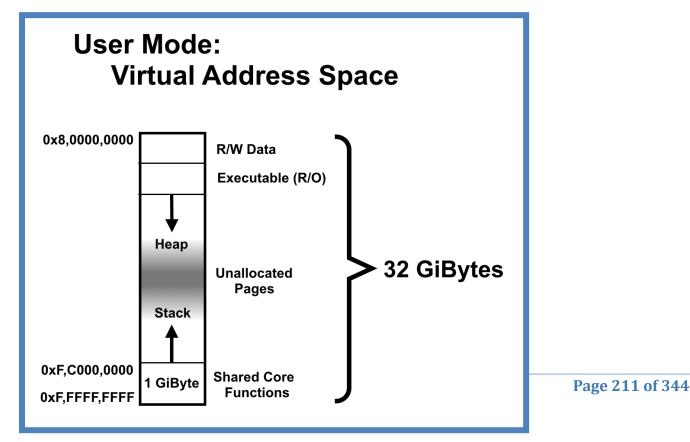

Typically, the global data will be placed at the beginning of the virtual address space, i.e., at address 0x8\_0000\_0000. Therefore, register gp will contain 0x8\_0000\_8000 which is the start of virtual memory, plus 2 pages (i.e., plus 32 KiBytes), allowing access to the first 4 pages of virtual memory. Register gp will remain constant during the execution of the program.

The "**link register**" (register **lr**, i.e., **r14**) is used in function/method invocation. The CALL instruction will store the return address in register "lr" and the RET instruction will jump back to that address. If the function/method is a leaf routine (i.e., if it doesn't invoke other functions/methods) then the return address can remain in lr until the RET instruction causes the return. Otherwise, the value of lr must be saved somewhere, typically on the stack, and retrieved before the return.

The "stack pointer register" or "stack top" (register sp, i.e., r15) points to the runtime stack. By convention, the stack grows downward from high memory (larger addresses) toward low memory (smaller addresses). By convention, sp will point to the first byte of the stack, i.e., the most significant byte of the doubleword sitting at the top of the stack. By convention, the stack will always grow in multiples of 8. In other words, sp will always contain a doubleword aligned address.

<sup>&</sup>lt;sup>1</sup> In fact, s0...s2 were originally callee-saved with the "s" standing for "saved".

<sup>&</sup>lt;sup>2</sup> In programs which have only a single thread and no need for a thread pointer, this register might instead be used as a callee-saved register. But beware that called functions will likely use this register to locate various parameters; using register tp as a callee-saved register is not practical.

Although floating point instructions are defined, there are no separate **floating point registers**. Instead, floating point data is kept and manipulated in the general purpose registers.

There is a **program counter (PC)** whose size is 36 bits.

Thus, the PC can contain any number within 0x0\_0000\_0000 ... 0xF\_FFFF\_FFFF. Any attempt to load the PC with a number outside this range is legal: bits [63:36] will be ignored with no overflow exception signaled.

**Commentary** Many processor ISAs include a "condition code register." Such a register usually contains bits such as:

- Sign / Negative Value

- Zero / Equal

- Carry Bit

- Overflow

In such ISAs, there is usually a COMPARE instruction (which will set bits in the status register) and several BRANCH instructions (which will test the status register bits and conditionally jump).

The normal pattern of most code is to execute a COMPARE instruction and, immediately afterward, execute a BRANCH instruction. They go together and effectively perform a single "test-and-jump" operation.

Blitz-64 does not include a "condition code register." Instead, the BRANCH instructions will perform both the test and the conditional jump. By combining them into a single instruction, greater performance efficiency can be achieved whenever this "test-and-jump" operation must be performed.

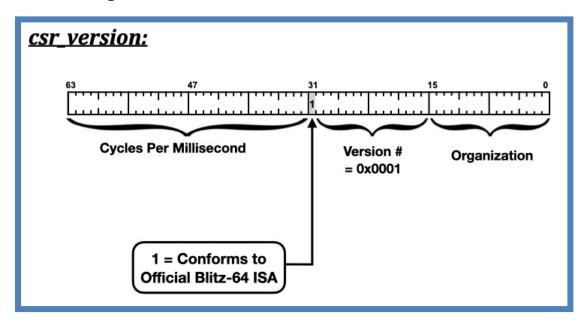

### **Control and Status Registers (CSRs)**

The "Control and Status Registers" (CSRs) are used by the protection and privilege system. The privilege system is used by the OS kernel to protect itself and manage

user-level processes. The CSRs are also used for interrupt processing, thread switching, and virtual memory manipulation.

At any moment, the processor will be executing either in "**user mode**" or in "**kernel mode**". OS kernel code is executed in kernel mode and application programs are executed in user mode.

Each instruction is either "**privileged**" or "**non-privileged**". When the core is running in user mode, only non-privileged instructions may be executed. When running in kernel mode, all instructions are usable.

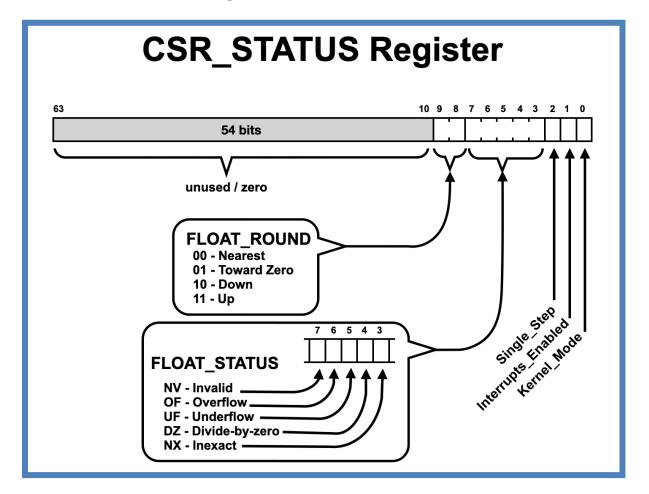

Changing the privilege mode is accomplished by writing to a CSR. A single bit in the status register (**csr\_status**) determines the current privilege mode.

CSRs can only be read/written when running in kernel mode.

There are 16 CSRs.

Each CSR has a special name and each has a unique function. Reading and/or writing a CSR will have an effect on the processor operation. The CSRs are read and written with just a couple of general-purpose instructions. The instructions to read/write the CSRs are privileged and can only be executed in kernel mode.

In order to understand the user-mode instruction set and to create user-level code, the CSRs can and should be ignored, especially on your first introduction to Blitz-64.

### <u>Virtual Memory</u>

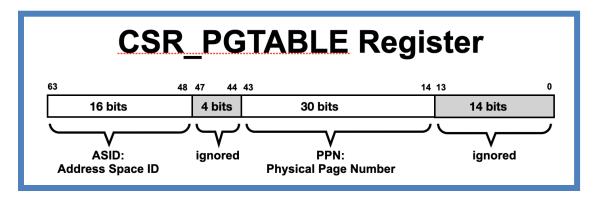

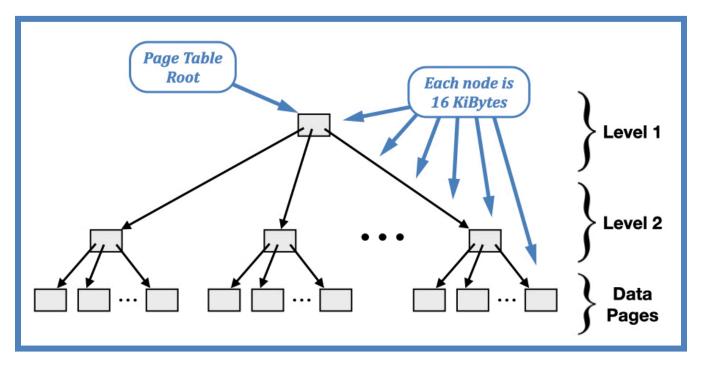

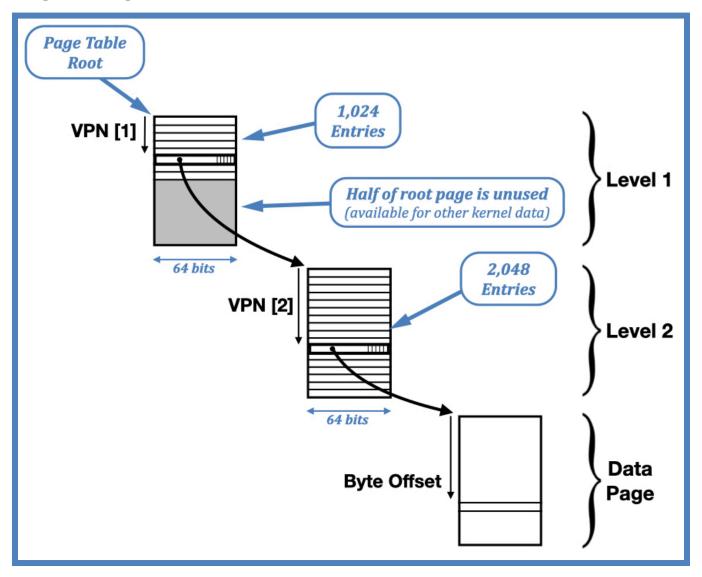

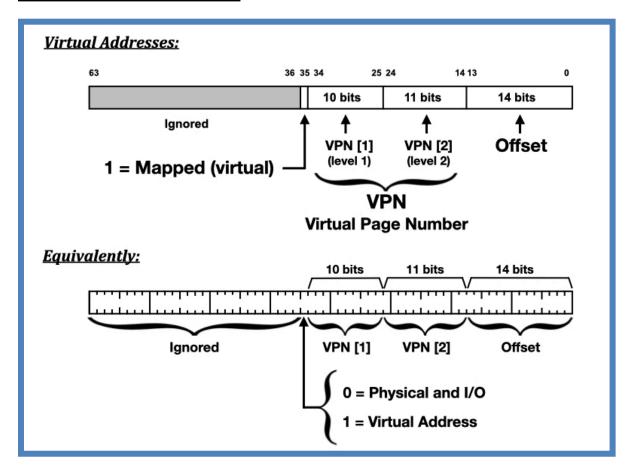

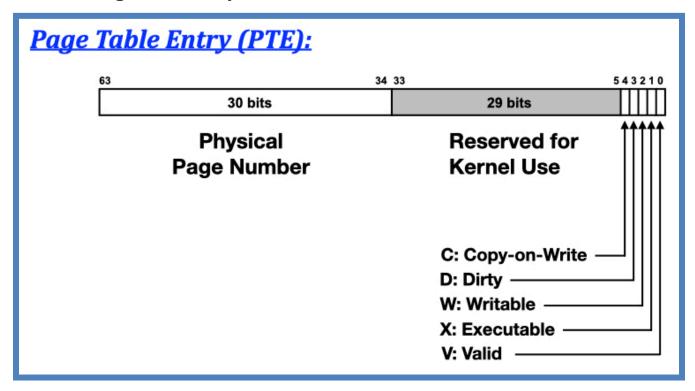

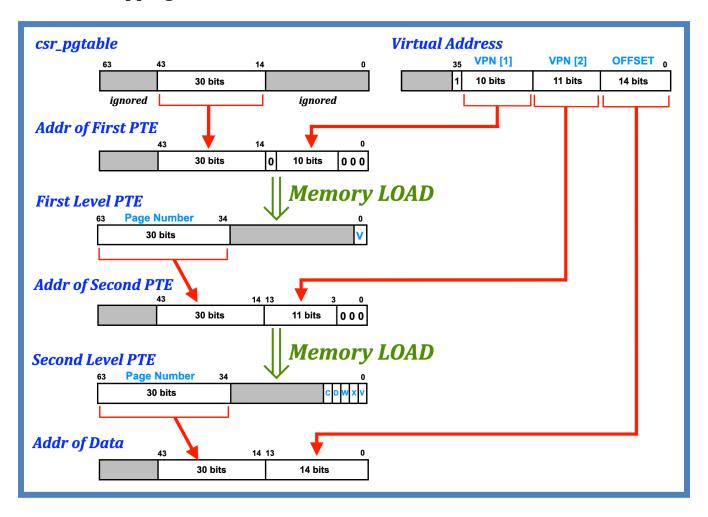

Blitz-64 supports virtual memory. For each virtual address space, there will be a page table stored in memory. The page table is organized as a tree of nodes and, at any time, the root of the current page table is pointed to by a control and status register (CSR) named **csr\_pgtable**.

Pages in the virtual address space can be marked as

- valid / invalid

- writable

- executable

- copy-on-write

- dirty

Any attempt by user code to access a page in violation of the permissions for that page will cause an exception.

The virtual memory architecture and page tables are described in the chapter titled "Memory, Address Spaces, and the Page Table".

# **Chapter 4: Instruction Formats**

### **Quick Summary**

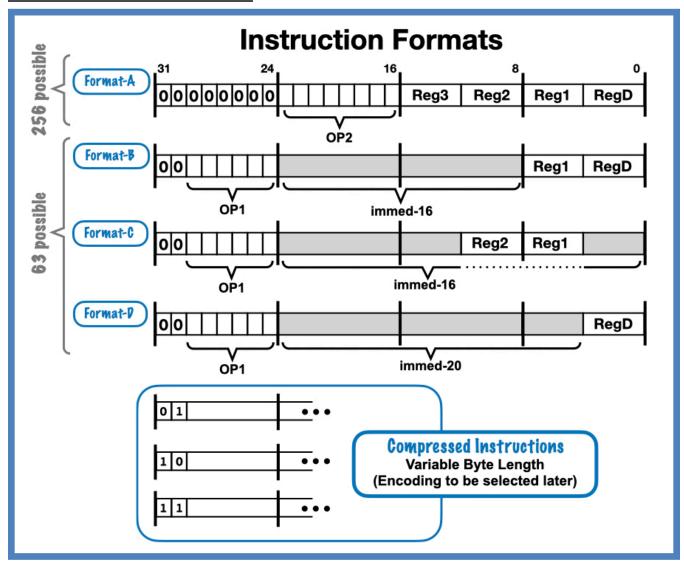

Machine instructions are 32 bits long.

The 16 registers are encoded in fields of 4 bits.

Immediate values occupy fields of either 16 or 20 bits.

- There are 4 formats of instructions, called A, B, C, and D.

- Assembly syntax is summarized.

The destination register is schematically called "RegD".

The operand registers are schematically called "Reg1", "Reg3", and "Reg3".

• Compressed instructions will be defined and specified in the future.

Compressed instructions are variable in length.

Compressed and full-sized instructions can be distinguished by their opcodes.

# **Compressed and Full-Sized Instructions**

There are two types of instructions:

- Full-sized instructions (32 bits)